从FAB到封装:硅通孔(TSV)的应力,让你的周边电路性能下降了多少?

在三维集成技术中,TSV通过垂直互连实现高密度封装,但制造过程中的热应力会显著改变周围硅衬底的晶体结构,导致载流子迁移率下降和电路性能波动。这种应力在FAB工艺中(如深孔刻蚀和铜填充)产生,并延续至封装阶段。若未提前补偿,局部器件可能出现明显迁移率变化,并在敏感路径上表现为性能下降。

? 应力根源:

工艺与材料的“隐形杀手” TSV应力主要源于两方面:

材料热失配:铜填充物与硅衬底的热膨胀系数差异显著,升温(如退火或封装键合)时产生压缩应力,冷却后形成残余应力区。

工艺缺陷:深孔刻蚀的垂直度偏差、绝缘层/阻挡层覆盖不均匀,或填充空洞会加剧应力集中。尤其在较大尺寸TSV(如部分MEMS场景)中,应力影响范围可扩散至几微米规模,对周围应力敏感的晶体管沟道造成干扰。

? 解决方案:从设计到工艺的应力“卸载术”

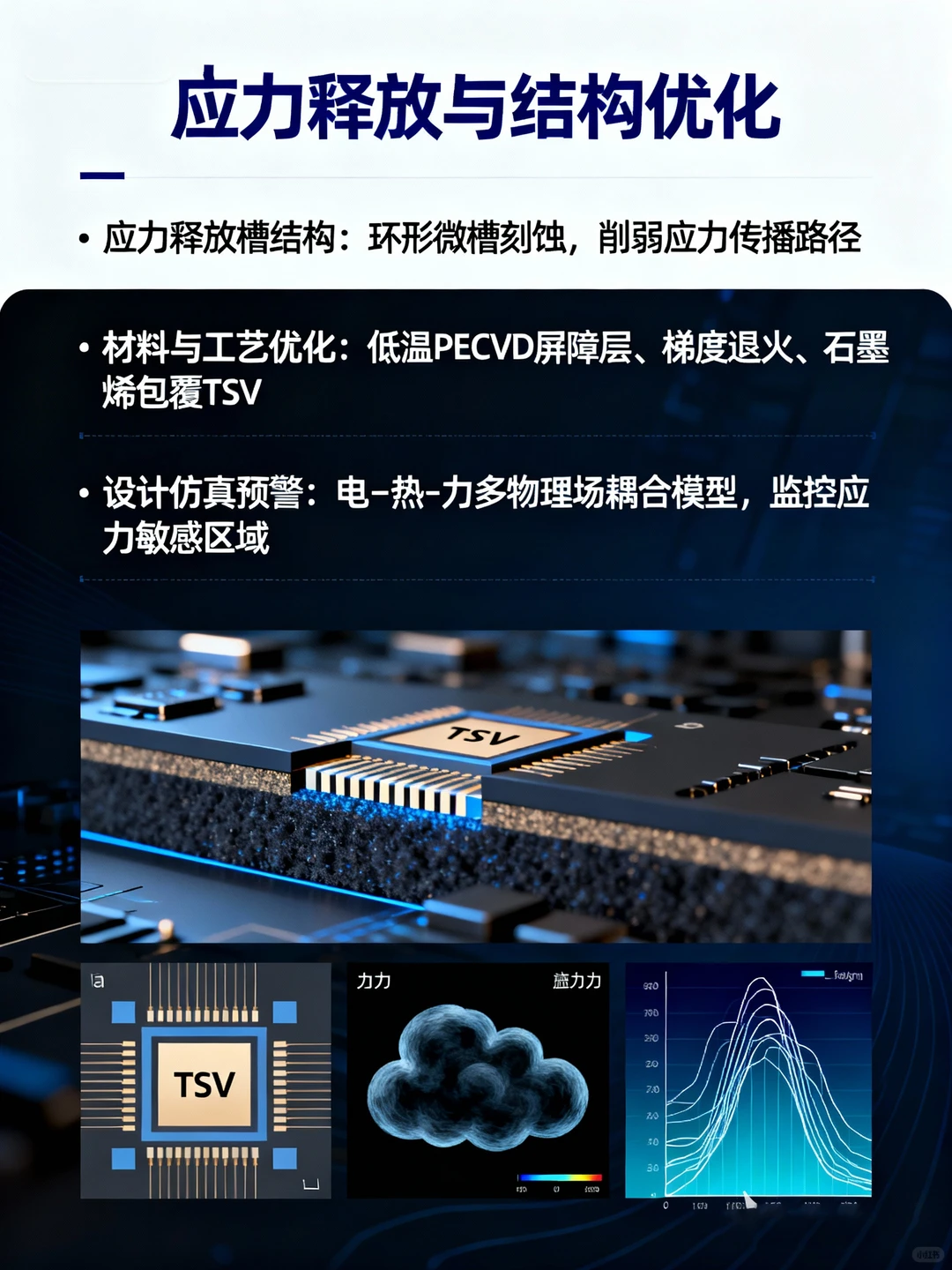

应力释放槽结构

在TSV周围刻蚀环形微槽(宽度约1~3μm,深度略高于周边介质层),可起到削弱应力传播路径的作用,使局部表面残余应力显著降低。需通过仿真优化槽体位置:通常在偏离TSV中心数微米处效果更好,同时避免削弱局部机械强度。

材料与工艺协同优化

低温沉积屏障层:采用等离子体增强化学气相沉积(PECVD)生成氮化硅等薄膜,可降低热预算、减小热应力;

梯度退火工艺:利用分阶段升温与缓冷策略,可逐步释放界面热应力并提升铜填充致密度;

石墨烯包覆TSV:属于研究方向之一,一些实验工作显示在电阻与热膨胀匹配方面有潜在优势,但尚未进入量产应用。

设计阶段仿真预警

建立电-热-力多物理场耦合模型,重点监控:

载流子迁移率映射图:标识应力敏感区域,优化周边电路布局;

缓冲器协同设计:通过合理布设分布式缓冲器补偿局部延时波动,部分仿真结果显示可减少缓冲器数量的同时维持时序稳定。

✅ 量产校验:

数据驱动的应力管控 实际量产中,通过晶圆级应力测试结构(如压阻式应力传感器)监测应力分布,并结合缺陷检测定位异常TSV。已有量产实践显示,在引入应力控制结构和工艺优化后,器件一致性和良率可获得明显改善,同时时钟偏移与跨区性能波动也更易受控。

#TSV应力优化 #三维集成技术 #半导体可靠性 #异构集成 #先进封装故障预防

在三维集成技术中,TSV通过垂直互连实现高密度封装,但制造过程中的热应力会显著改变周围硅衬底的晶体结构,导致载流子迁移率下降和电路性能波动。这种应力在FAB工艺中(如深孔刻蚀和铜填充)产生,并延续至封装阶段。若未提前补偿,局部器件可能出现明显迁移率变化,并在敏感路径上表现为性能下降。

? 应力根源:

工艺与材料的“隐形杀手” TSV应力主要源于两方面:

材料热失配:铜填充物与硅衬底的热膨胀系数差异显著,升温(如退火或封装键合)时产生压缩应力,冷却后形成残余应力区。

工艺缺陷:深孔刻蚀的垂直度偏差、绝缘层/阻挡层覆盖不均匀,或填充空洞会加剧应力集中。尤其在较大尺寸TSV(如部分MEMS场景)中,应力影响范围可扩散至几微米规模,对周围应力敏感的晶体管沟道造成干扰。

? 解决方案:从设计到工艺的应力“卸载术”

应力释放槽结构

在TSV周围刻蚀环形微槽(宽度约1~3μm,深度略高于周边介质层),可起到削弱应力传播路径的作用,使局部表面残余应力显著降低。需通过仿真优化槽体位置:通常在偏离TSV中心数微米处效果更好,同时避免削弱局部机械强度。

材料与工艺协同优化

低温沉积屏障层:采用等离子体增强化学气相沉积(PECVD)生成氮化硅等薄膜,可降低热预算、减小热应力;

梯度退火工艺:利用分阶段升温与缓冷策略,可逐步释放界面热应力并提升铜填充致密度;

石墨烯包覆TSV:属于研究方向之一,一些实验工作显示在电阻与热膨胀匹配方面有潜在优势,但尚未进入量产应用。

设计阶段仿真预警

建立电-热-力多物理场耦合模型,重点监控:

载流子迁移率映射图:标识应力敏感区域,优化周边电路布局;

缓冲器协同设计:通过合理布设分布式缓冲器补偿局部延时波动,部分仿真结果显示可减少缓冲器数量的同时维持时序稳定。

✅ 量产校验:

数据驱动的应力管控 实际量产中,通过晶圆级应力测试结构(如压阻式应力传感器)监测应力分布,并结合缺陷检测定位异常TSV。已有量产实践显示,在引入应力控制结构和工艺优化后,器件一致性和良率可获得明显改善,同时时钟偏移与跨区性能波动也更易受控。

#TSV应力优化 #三维集成技术 #半导体可靠性 #异构集成 #先进封装故障预防