前一篇笔记写过了这次流回来的VCO测试碰到的问题,很多前辈给出了有价值的想法非常感谢。这个周去仿真➕测试重点尝试了一下几个方面,现在更新下(我不会重新编辑小红书笔记,所以新开一篇……)

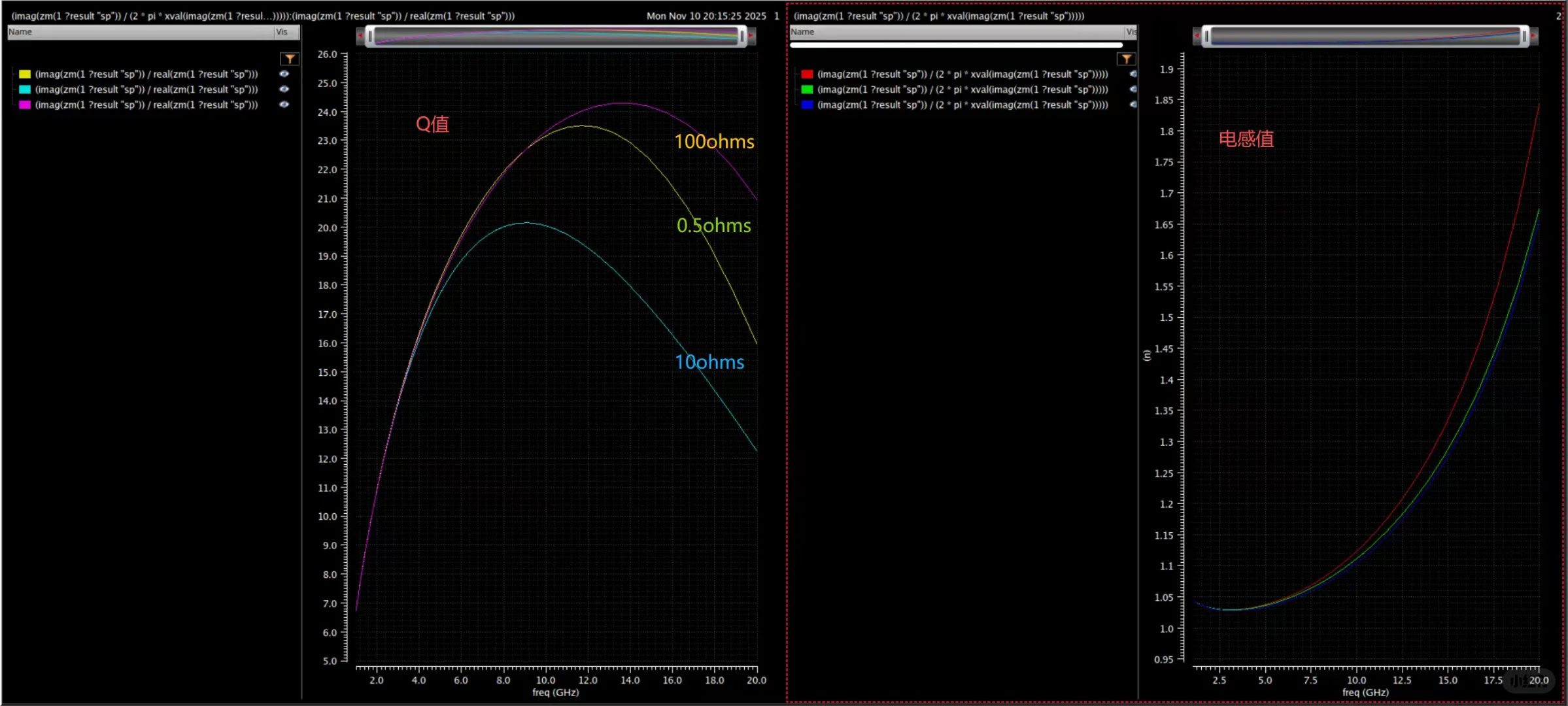

第一是有位前辈提出了对于"频率升高、相噪恶化"可能性的原因——因为这次忘记在电感底部添加低掺杂衬底标示层(psub),所以实际流出来的感值会因为涡流感应减小而Q值也因为涡流损耗变大而降低。我查阅了一些材料,里面提到一般工艺做晶体管使用的衬底电阻率在0.1~1ohm/cm之间,而轻掺杂的衬底电阻率更高,大概在10ohm/cm。而后查阅了EMX里的. proc文件,里面清晰的写着sub的电阻率正是10ohm/cm。

因此我认为,这个工艺下为了仿测一致必须得铺psub层,这是厂商为EMX提取提供的默认设置。我尝试了改动. proc里关于sub电阻率的定义,却发现了异常情况——如0.5ohm/cm比10ohm/cm的Q值更好,我将0.5改成了0.0001重新提也是这样,按理来说这时候Q值应该差的没法看了才对(相当于在电感底下铺了层金属)。。目前这一点还没找到原因,可能是这个定义的参数并没有正确的用在提取之中?

进一步打算是移植到HFSS里,更改衬底电阻率参数验证。现在正在学. gds导入HFSS……另外我觉得其实在6GHz这个涡流对Q值影响并没有那么显著,可能会对频率升高有影响,但是绝不可能让相噪恶化20dB。

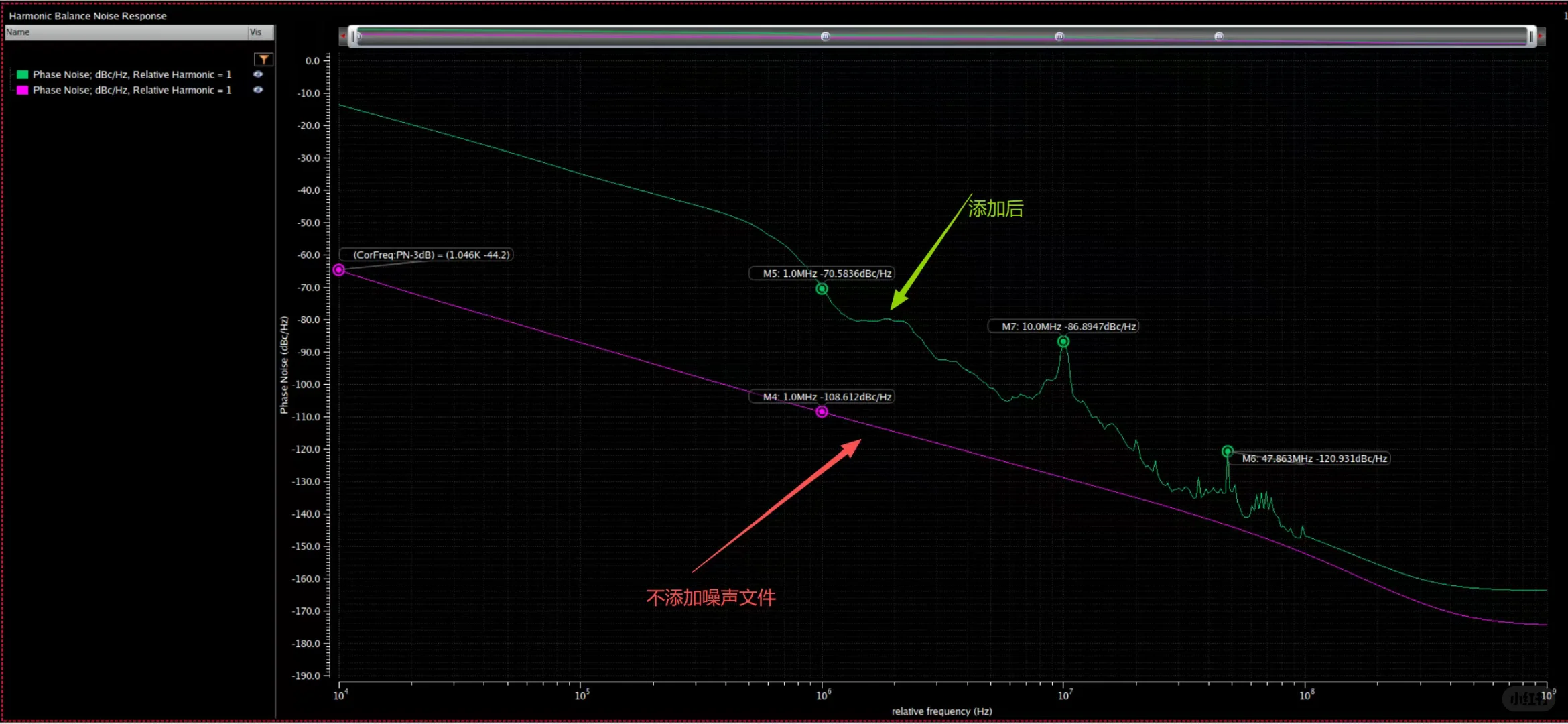

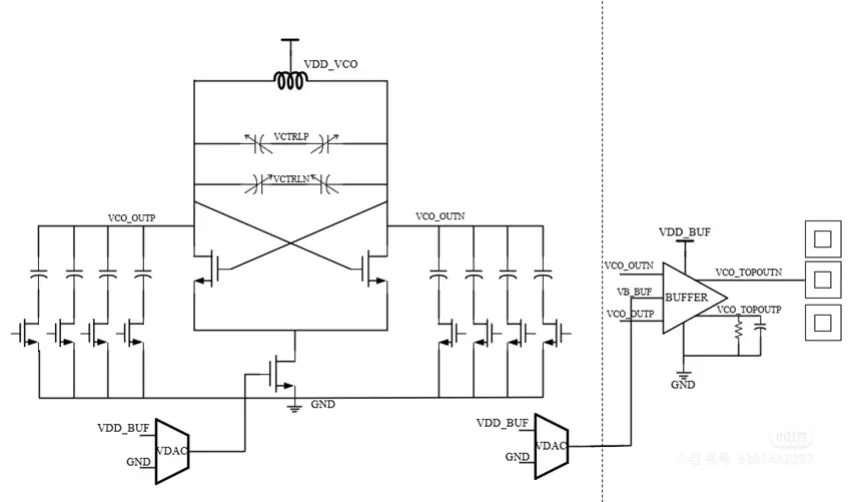

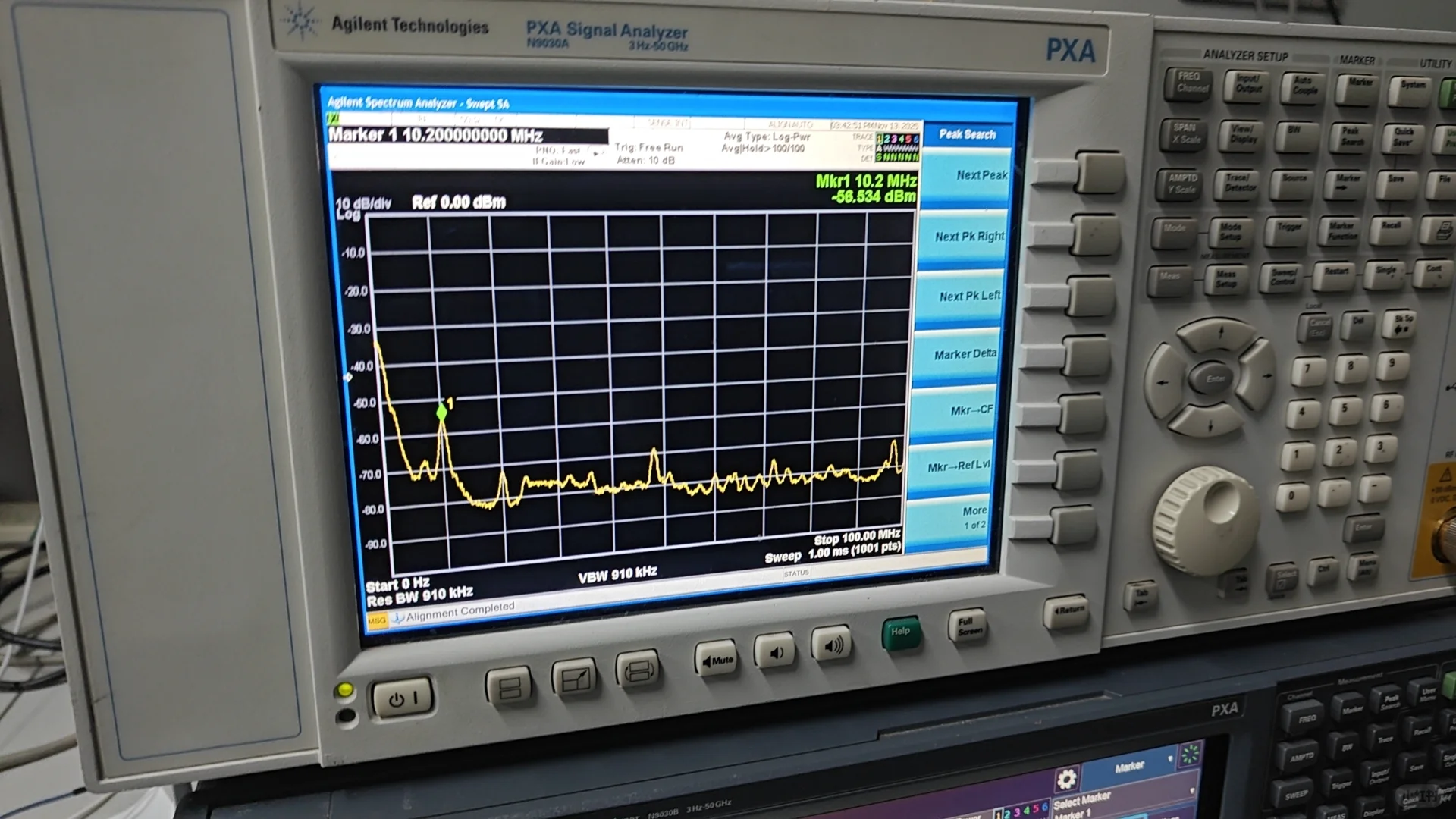

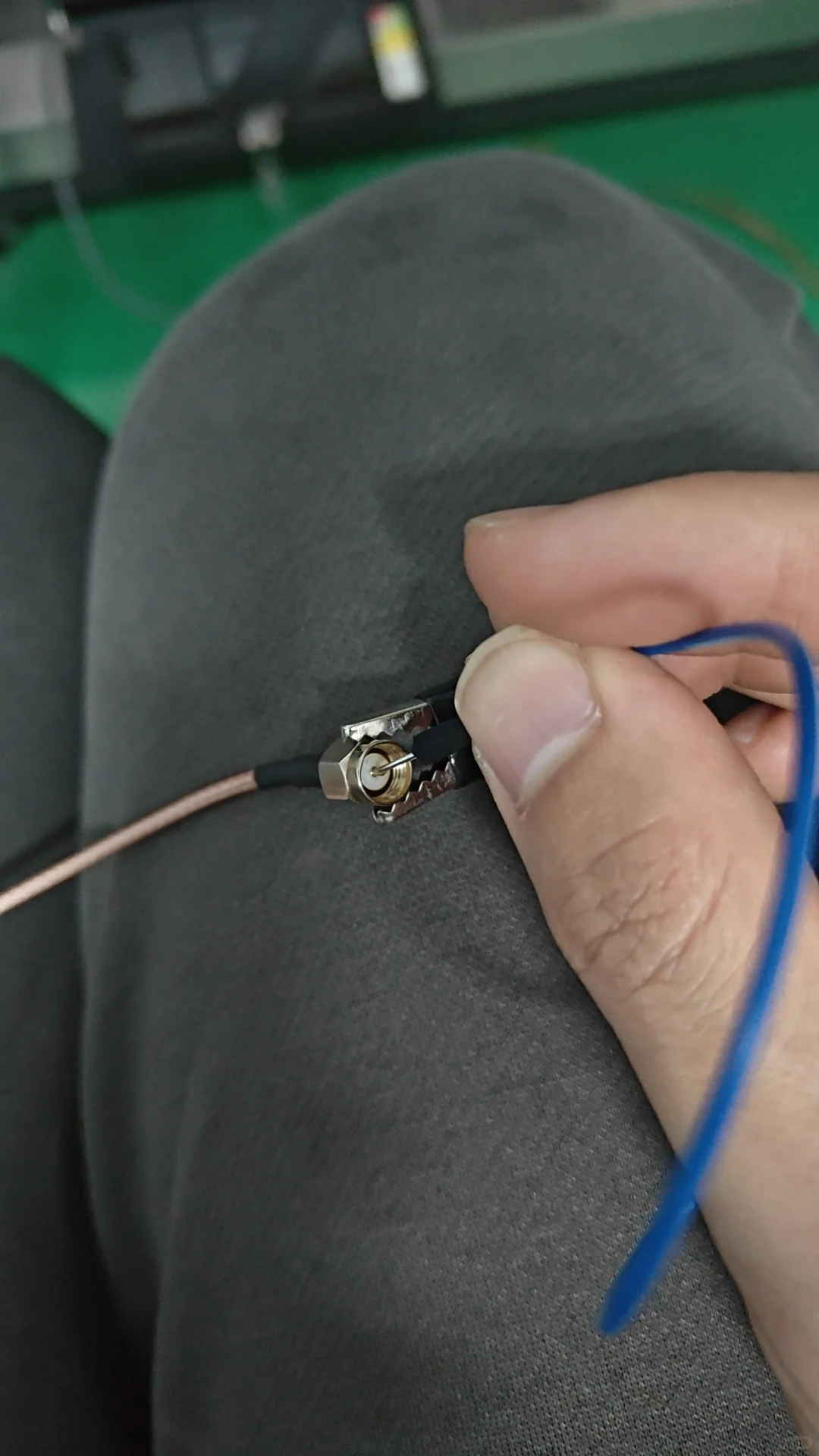

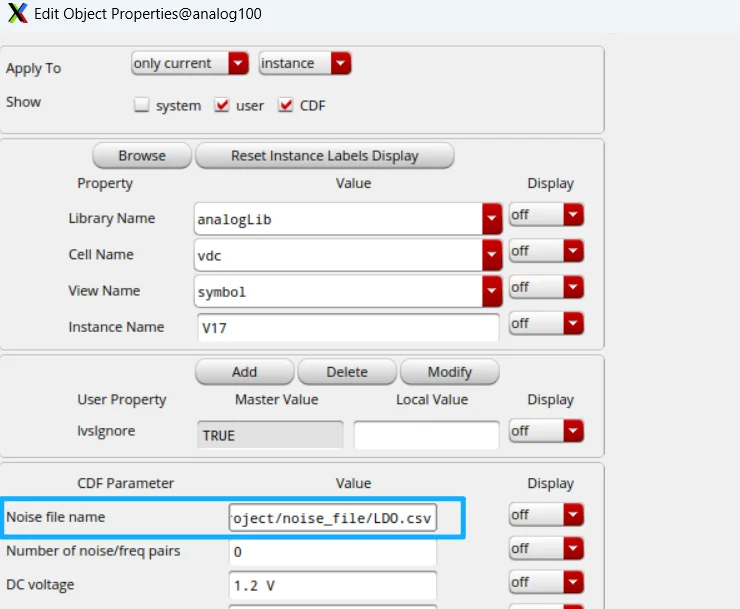

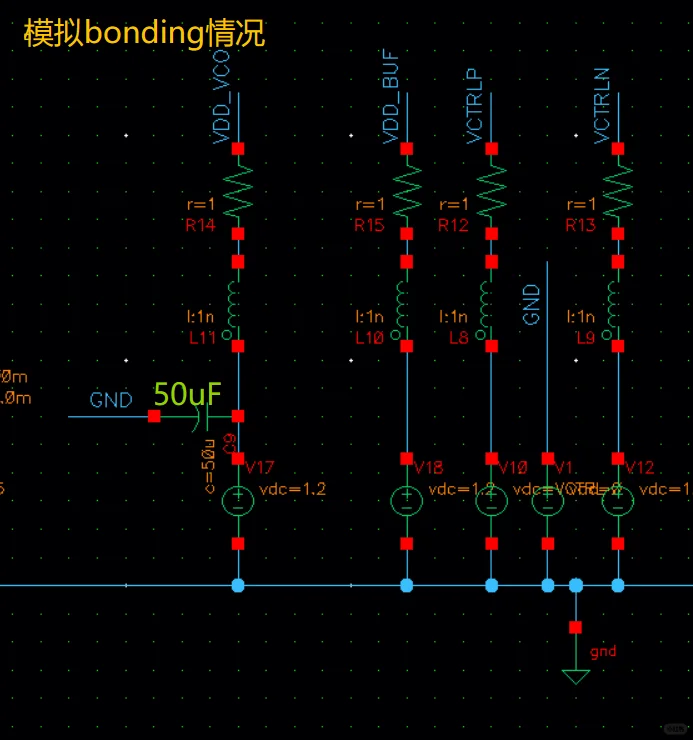

第二是一位前辈让我接频谱仪直接得到LDO的噪声数据,并把bonding和外部负载放进仿真验证。LDO的频谱见图三,我也不知道为什么我们这个LDO的输出为什么那么差,我接频谱仪的时候是这跟SMA接口的线外面用鳄鱼夹到地,里面用杜邦线接触LDO电源板的输出(还是挺费劲的),频谱仪处接了个很大的DCBLOCK,看到大概10MHz这有个明显的杂散。另外因为VCO的电压控制端是用安捷伦的电压源直接给上的,所以我也测了电压源的输出频谱,长得跟LDO差不多,所以我有点怀疑是不是这个电压源本身就不对劲?总之拿了数据回来,进行了一番数据处理,就把noise. csv直接带到了仿真里面,感觉得到的结果跟测试还是挺吻合的……所以在想有没有合适的解决方案(并大电容50uF都没用)

以及VCO有没有些合适的能抑制电源噪声传递的结构呢?现在VCO那不考虑其他的,电感肯定是直接就把电源噪声传到输出了,变容管那也是,直接关系到了频谱的纯净性。然后那个共源的Buffer因为是个伪差分,所以电源抑制比肯定也不好 #模拟IC #射频IC#VCO

第一是有位前辈提出了对于"频率升高、相噪恶化"可能性的原因——因为这次忘记在电感底部添加低掺杂衬底标示层(psub),所以实际流出来的感值会因为涡流感应减小而Q值也因为涡流损耗变大而降低。我查阅了一些材料,里面提到一般工艺做晶体管使用的衬底电阻率在0.1~1ohm/cm之间,而轻掺杂的衬底电阻率更高,大概在10ohm/cm。而后查阅了EMX里的. proc文件,里面清晰的写着sub的电阻率正是10ohm/cm。

因此我认为,这个工艺下为了仿测一致必须得铺psub层,这是厂商为EMX提取提供的默认设置。我尝试了改动. proc里关于sub电阻率的定义,却发现了异常情况——如0.5ohm/cm比10ohm/cm的Q值更好,我将0.5改成了0.0001重新提也是这样,按理来说这时候Q值应该差的没法看了才对(相当于在电感底下铺了层金属)。。目前这一点还没找到原因,可能是这个定义的参数并没有正确的用在提取之中?

进一步打算是移植到HFSS里,更改衬底电阻率参数验证。现在正在学. gds导入HFSS……另外我觉得其实在6GHz这个涡流对Q值影响并没有那么显著,可能会对频率升高有影响,但是绝不可能让相噪恶化20dB。

第二是一位前辈让我接频谱仪直接得到LDO的噪声数据,并把bonding和外部负载放进仿真验证。LDO的频谱见图三,我也不知道为什么我们这个LDO的输出为什么那么差,我接频谱仪的时候是这跟SMA接口的线外面用鳄鱼夹到地,里面用杜邦线接触LDO电源板的输出(还是挺费劲的),频谱仪处接了个很大的DCBLOCK,看到大概10MHz这有个明显的杂散。另外因为VCO的电压控制端是用安捷伦的电压源直接给上的,所以我也测了电压源的输出频谱,长得跟LDO差不多,所以我有点怀疑是不是这个电压源本身就不对劲?总之拿了数据回来,进行了一番数据处理,就把noise. csv直接带到了仿真里面,感觉得到的结果跟测试还是挺吻合的……所以在想有没有合适的解决方案(并大电容50uF都没用)

以及VCO有没有些合适的能抑制电源噪声传递的结构呢?现在VCO那不考虑其他的,电感肯定是直接就把电源噪声传到输出了,变容管那也是,直接关系到了频谱的纯净性。然后那个共源的Buffer因为是个伪差分,所以电源抑制比肯定也不好 #模拟IC #射频IC#VCO